莫坤龙,GRL东莞 实验室经理

提起PCIe接口,可以说它在我们日常工作和生活中无处不在。如我们常见的电脑主板,显卡,存储类的记忆体,甚至是网卡等消费电子都应用到了PCIe接口。不知道大家有没有发现,从PCIe3.0到PCIe4.0的迭代耗时有7年多之久。但近年随着消费电子、数据中心及人工智能的高速发展,PCIe标准的发展也在随之进入快车道,迭代耗时也越来越短。目前PCIe 5.0已经趋于成熟,虽然PCIe 6.0仍然有一些标准(如CEM,PHY)还在讨论中,但PCI-SIG也在同步推进PCIe 7.0标准。

以上是PCIe标准近期的更新,以下内容则主要和大家一同交流PCIe 6.0技术的更新及一致性测试等内容。

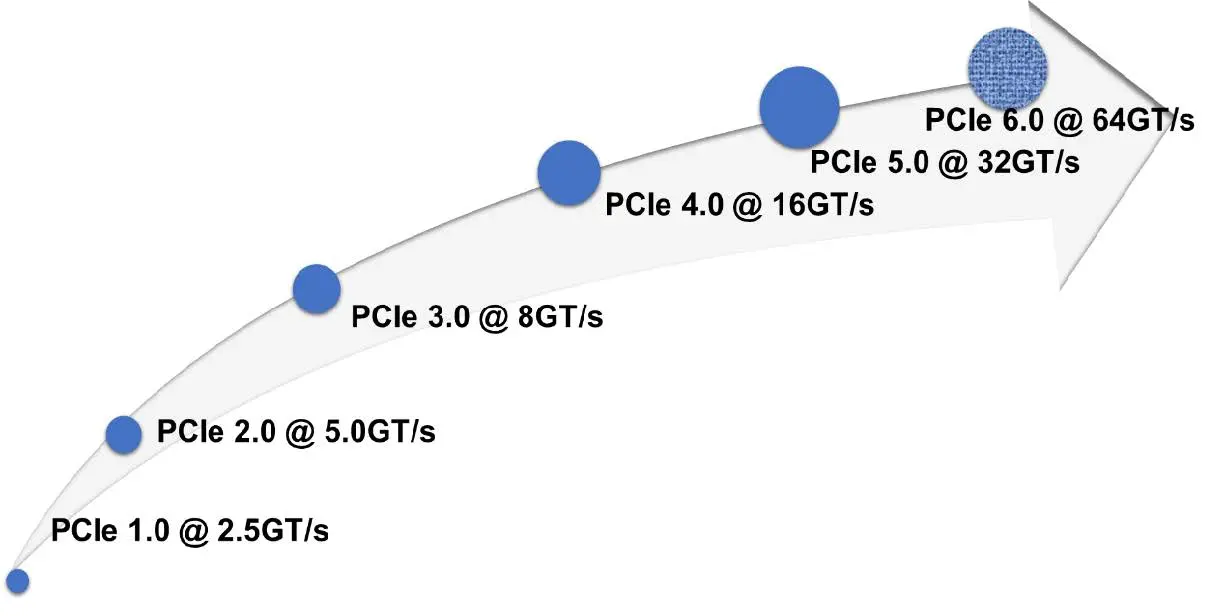

从PCIe1.0 到PCIe6.0,随着需求不断迭代的PCIe接口

大家都知道PCIe(Peripheral Component Interconnect Express)是高速串行计算机扩展总线标准,旨在替代原来的PCI。目前由PCI-SIG(PCI Special Interest Group)负责标准制定和推广,PCI-SIG标准自2003年推到PCIe 1.0版本以来,到2021年PCIe 6.0发布,传输能力也从开始的2.5GT/s进化到64GT/s。

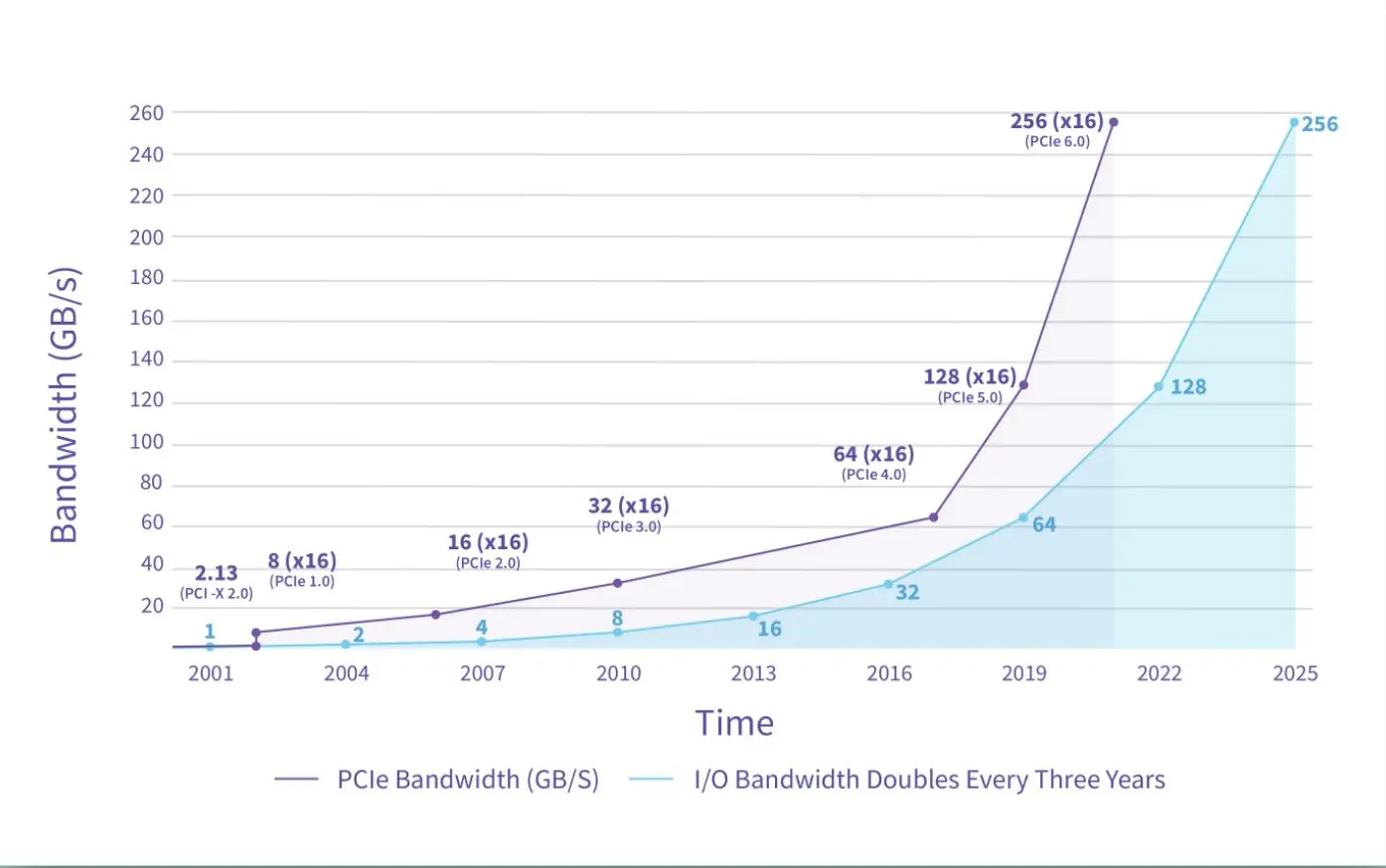

图1:PCIe传输带宽变化(来源: PCI-SIG)

图2:PCIe传输容量变化(来源: PCI-SIG)

我们可以从图1、图2中可见,PCIe接口的速率几乎每一代都在翻倍,每一代PCIe技术都在寻求在保持传输带宽不变的情况下,实现速率翻倍的方法。PCIe 6.0也不例外。因此,我们可以看到这次PCIe 6.0标准与之前标准相比,最大的变化就是信号的调制方式改为PAM4模式来传输,下面我们来简单对比一下NRZ和PAM4信号的区别。

不同于 NRZ 编码,PCIe 6.0 采用 PAM4 编码方式

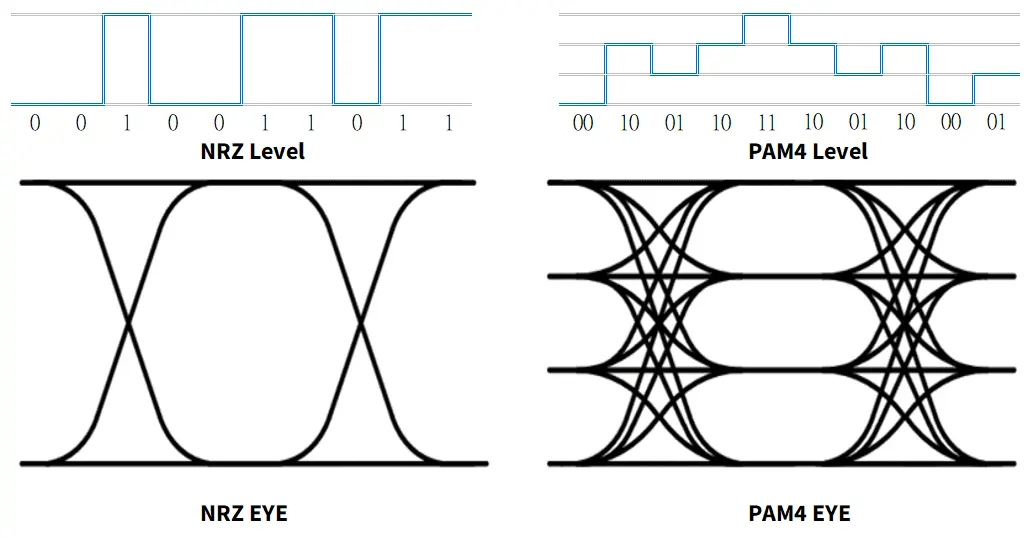

图3:NRZ vs PAM4电平和眼图

NRZ,不归零调制(Non-Return-to-Zero),是PCIe 1.0至PCIe 5.0所采用的调制方式。在新一代的PCIe 6.0中,并未采用传统的NRZ,而是采用了PAM4调制,即四电平脉冲幅度调制(Pulse Amplitude Modulation 4-levels)。

如图三所示的对比可以看出,NRZ只有0,1两个电平,形成一个眼,而PAM4会有0,1,2,3共4个电平,形成了3个眼。所以PAM4每个符号能携带2个bit的信息,比NRZ每个符号只能携带1个bit信息,传输能力提高了一倍。

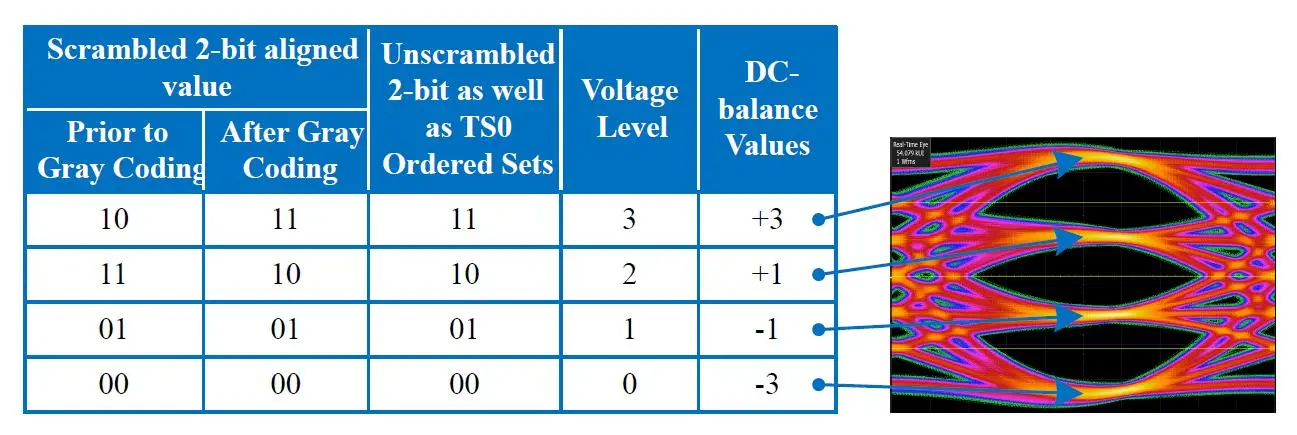

图4:PAM4信号的UI Level(来源:PCIe Base Spec Revision 6.0.1)

PCIe 6.0的调制改为PAM4还有另一个优势的地方,就是传输64GT/s的速率,依然可以和PCIe 5.0的奈奎斯特频率(Nyquist Frequency)保持一致,而通道IL从PCIe 5.0的36 dB变为了PCIe 6.0的32 dB,所以这从另一个角度来看,PAM4还有助于降低通道的损耗。从以上图4可知,PAM4的4个电平(Level0,1,2,3)进行格雷编码(Gray Coding),4个电平对应的格雷编码分别是00,01,11,10,格雷编码的方式是要求相邻符号,每次只能变化一位,且首尾符号也只是变化一位,这样的编码方式可以有效改善误码率。PAM4信号里还定义了4个电平的DC Balance Values,以满足直流平衡设计需求。另外,虽然PCIe 6.0采用了PAM4的调制,但PCIe 6.0依然向下兼容之前所有版本的速率。

PCIe 6.0的特性与优势

PCIe6.0调制方式的改变,带来速率的翻倍以及更高的传输效率。但由于PAM4有4个电平的幅度,相比NRZ的模式,每个眼睛(Eye)的幅度降低了很多,所以信号的传输过程中对噪声更敏感,也更容易产生突发误码。这也给PCIe 6.0在信号完整性方面带来挑战,不仅要求更高的信噪性比,且随着眼高的降低对接收端灵敏度等方面具备更高的要求

PCIe 6.0的特性:FBER (First Bit Error Rate)、FEC (Forward Error Correction)机制与流量控制单元(Flow Control Unit)

在PCIe 5.0的NRZ时代,BER(Bit Error Rate)目标值要求是10-12。但在PCIe 6.0表征误码率时会出现一个新的名词FBER(First Bit Error Rate),PCIe 6.0规范FBER要求小于10-6,此处的FBER是没有把任何的突发误码计算进去的。

对于高速率传输的信号,特别是到了PAM4调制时代,往往会出现比较高的误码率无法达到规范要求,所以我们可以看到PCIe 6.0引入了前向纠错FEC(Forward Error Correction)机制,前向纠错是信号在发端时就加入额外特定的冗余信息,当传输发生错误时,FEC机制可以在接收端把错误纠正过来以达到改善误码率效果,另外,轻量级FEC还可以保持PCIe 6.0信号传输的超低时延。但需要注意的是,FEC的纠错能力也是有限的,如果是发生大量的错误,FEC也可能无法纠正。

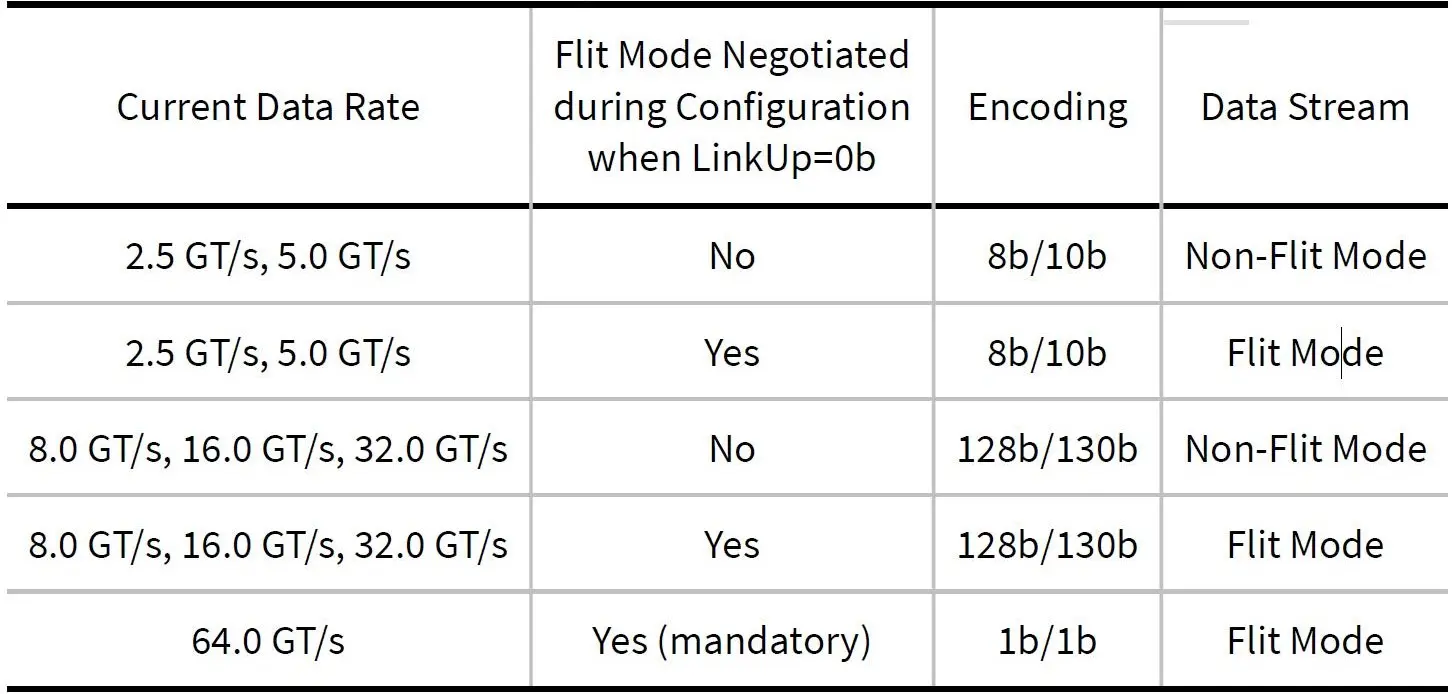

PCIe 6.0还具有流量控制单元(Flow Control Unit)模式,且是固定数据包大小(Fixed Sized Code Words),相比之前版本的非Flit模式和编码方式,PCIe 6.0要求强制使用Flit 模式传输,编码方式也改成了1b/1b,这就意味着传输的每一位信息都是有效码,这有别于之前的8b/10b和128b/130b的传统编码。

另外,PCIe 6.0在能效方面是优于PCIe 5.0,PCIe 6.0具有全新的低功耗模式:L0p,它可以在保持数据流的情况下来灵活调节带宽,提高利用率,以达到降低功耗目的,这对服务器(Server)级应用来说是一个巨大的优势。

图5:有效的编码和数据流模式组合 (来源:PCIe Base Spec Revision 6.0.1)

PCIe 6.0的均衡方面,依然保持发送端使用FFE,接收端使用CTLE和DFE组合的架构,但由于前面提到的PAM4的调制格式,每个眼睛(Eye)的幅度降低,使得电平间的幅度间隔靠得更近了,所以可以看到PCIe 6.0 的DFE从PCIe 5.0的3-Tap变为了16-Tap,以补偿PAM4更容易产生码间干扰问题。

GRL PCIe 6.0自动化校准及解决方案

PCIe 6.0标准的基本规范 (Base Specification) 已经定稿,但Card Electromechanical (CEM) 规范和PHY 测试 Specification仍处于0.5版本的状态。

GRL紧随PCI-SIG协会的标准发展步伐,不仅可以提供包括PCIe 5.0及前几代的测试服务和解决方案,对于PCIe 6.0,GRL适时推出了GRL-PCIE6-BASE-RXA自动化校准及测试解决方案。

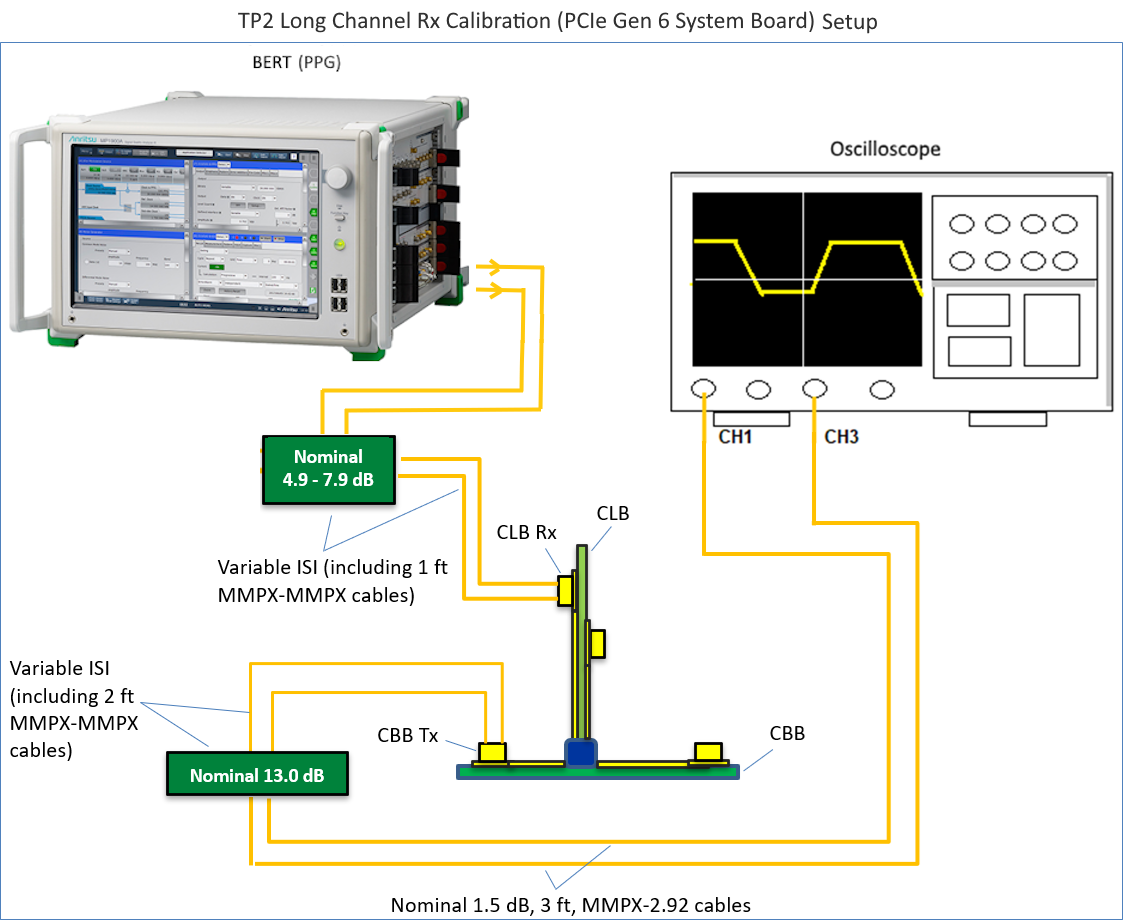

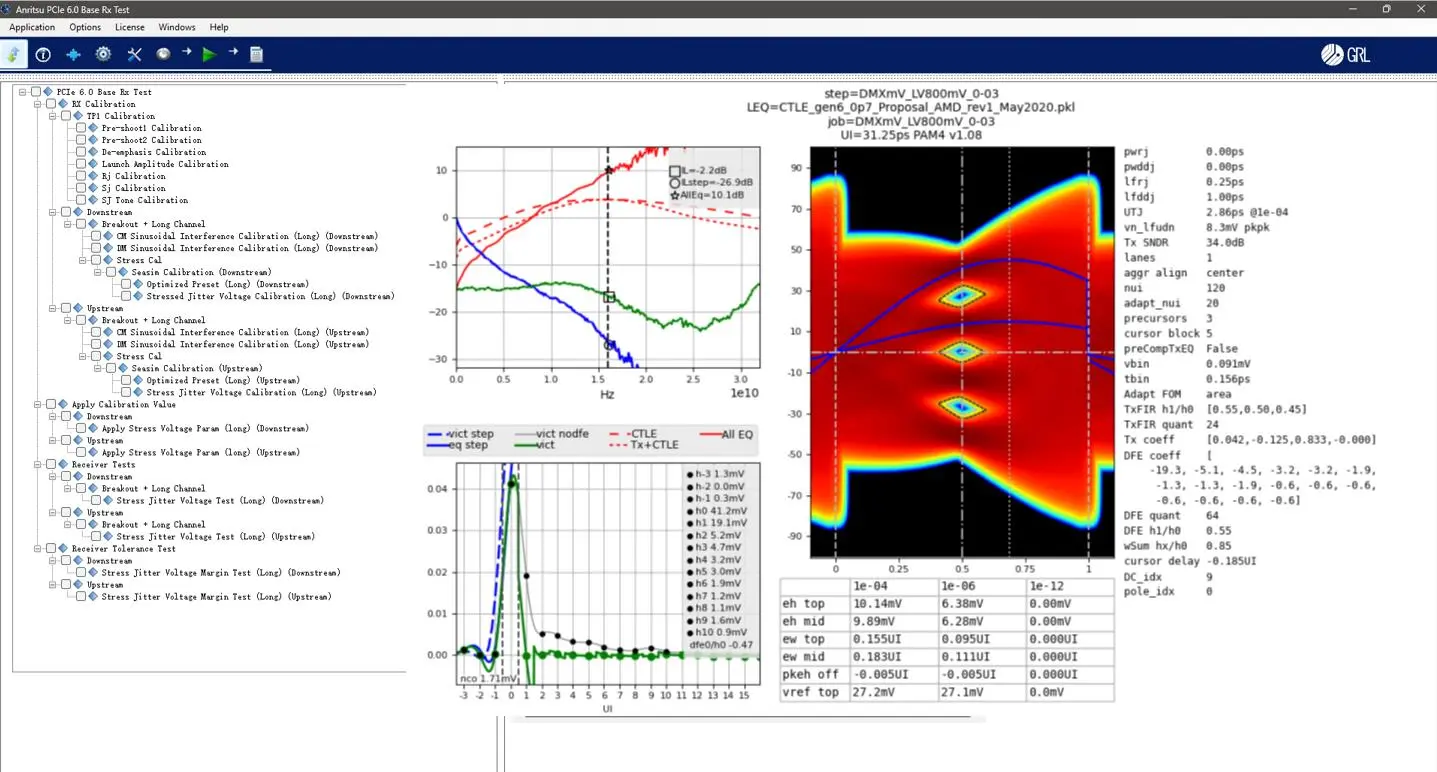

图6:GRL-PCIE6-BASE-RXA自动化校准及测试解决方案

结论

以上内容介绍了PCIe 6.0的相关情况,如新的调制方式,以及PCIe 6.0的一些新的特性,相信PCIe 6.0将会给使用者带来极致体验的同时,也会为生产及研发部门带来不一样的挑战。依据过往经验,在不远的将来就能够陆续刊登PCI6.0产品一致性测试需求,GRL也会紧随协会标准发展步伐,在PCIe的高速发展上,继续为客户提供更先进、更全面的测试服务及解决方案,提供更好的一站式服务体验。

参考

- PCI-SIG, PCI Express® Base Specification Revision 6.0.1

- Advancing Artificial Intelligence and Machine Learning Applications, Vamshi Kandalla, Granite River Labs

- GRL推出PCI Express® 6.0 接收端自动化校准及测试解决方案

作者

莫坤龙 Winson Mok

GRL东莞 实验室经理,在信号完整性和存储测试拥有多年的工作经验,熟悉Thunderbolt、PCI Express、USB及Ethernet等多种测试规格,目前负责GRL东莞Storage的测试。