从社群媒体到自动驾驶汽车和家用电器,人工智慧(AI)和机器学习(ML)得运算在大众的生活中比以往伴随更大得角色。已达 1000 亿美元得 AI 和 ML 市场预计在 2030年之前长到20倍的 2兆美元。而推动这庞大市场的技术是促进高频宽和低延迟资料传输通道的 PCI Express® (PCIe®) 5.0 架构。

PCI Express® (PCIe®) 5.0 架构有哪些新功能?

PCIe 5.0 于 2019 年 5 月发布,提供前版 PCIe 4.0 的两倍资料传输能量。这使得图形适配器卡、网路介面卡 (NIC)、储存加速器设备、固态硬碟 (SSD) 甚至是图形处理单元 (GPU)等 PCIe 周边装置展示更高层次的技术表现。

PCIe 5.0 如何支持 ML 和 AI 应用

至于为什么 PCIe 5.0 对 ML 和 AI 应用如此关键,我们先得知道下一代技术应用得要求:

- 能连接上多数得计算芯片和网络设备。这通用性也是 PCIe 等广泛互连协议经常用于实现加速器解决方案的原因。

- 标准软件和常用编程模型,便于设备发现、编程和管理。

- 软件必须易于开发。PCIe 的广泛采用使所有设备几乎可以立即部署。

可通过低延迟、不归零的物理层承载更多协议,使 CPU 能够随着 AI 和 ML 设备的激增跟上日益激增的数据量。

PCIe 5.0 能支持多快的数据传输?

目前,多数的处理器和主板都支持第4代 PCIe。该标准在 2017 年首次发布时具有划时代的意义。然而,许多用户开始遇到表现上的瓶颈。例如,采用 M.2 NVMe 外形的固态硬盘只能在四条通道上实现 8GB/s 的持续数据传输。而 PCIe 5.0 SSD 的速度则翻了一番,达到 16GB/s,32 通道设备的带宽为 128GB/s。

PCIe 5.0 所需组件

AMD 的 AM5 和 Intel 的 LGA 1700 主板等产品已经开始支持 PCIe 5.0,预计在近期还会有更多新产品投放市场。但要注意的是,只有在连接的两端都支持 PCIe 5.0 的情况下才能实现更高的数据传输速度。从理论上讲,与 PCIe Gen4 主板配对的 PCIe 5.0 SSD 能够以最大 Gen4 带宽(16GT/s)运行。因此,它能够在 x16 链路宽度上以 64GB/s 的速度传输数据。

如何影像设备开发?

为什么市场上的 PCIe 5.0 设备仍然如此之少?

不可否认的是,PCIe 5.0 是开发更快设备的必要条件。但它的存在本身并不能提高 GPU 或 SSD 的性能,尤其是已经拥有足够带宽的设备。事实上,尽管 PCIe 5.0 标准已发布四年,目前在市场上流通的 PCIe 5.0 设备并不多。

不过,PCIe 5.0 肯定会在顺序读写以及传输速度两方面的提高发挥关键作用,尤其是在传输较大文件的应用中。Crucial T700 和 SEAgate FireCuda 540 等第 5 代固态硬盘已经比第 4 代固态硬盘有了显著的改进。PCIe 第 5 代固态硬盘也开始浮出水面,不过在 PCIe 5.0 真正成为主流之前,还需要有更多经济实惠的组件。

PCIe 5.0 的成本局限

升级到 PCIe 5.0 的主要障碍在于成本。在大多数情况下,想兼容 PCIe 5.0 设备,主板、CPU 甚至是内存都需要升级。不同的主板对 PCIe 5.0 的支持程度也不同。因此,对用户来说,想要以低成本的方式升级也并不简单。此外,市场上较新的 PCIe 5 代固态硬盘需要散热片,甚至是像 Corsair MP700 Pro 固态硬盘的主动冷却解决方案。虽然散热片案例上是可选项,但硬件维护还是不可忽略的考虑因素。

PCIe 6.0 预计发布日期

考量到目前市场中最优秀的主板也不算是 100% PCIe 5.0,领域圈内者都认为 PCIe 6.0 将在 PCIe 5.0 成为标准的时期发布,导致消费者不断落后于最新技术规范。

PCIe 6.0 的发布日期到此尚未确定,但可以肯定的是,它将在 2025 年或 2026 年之间发布。这意味着 AM5 主板除了最后一个芯片组以外不会受被 PCIe 6.0 影响。

PCIe 5.0 设计挑战

较高频率的信号衰减

通道插入损耗(IL)造成的信号衰减是 PCIe 5.0 技术系统设计面临的最大挑战。最初的 PAM-4 方法用于速度超过 30 GT/s 的数据传输标准。

虽然 PAM 助于将信号的奈奎斯特(Nyquist)频率降低到数据传输的四分之一,但其代价是 9.5 dB 的信噪比(SNR)。PCIe 5.0 架构的不再使用 PAM-4 而是继续使用非归零(NRZ)信令方案,即信号的奈奎斯特频率为数据速率的二分之一。

PCIe 5.0 如何抵消偏差风险

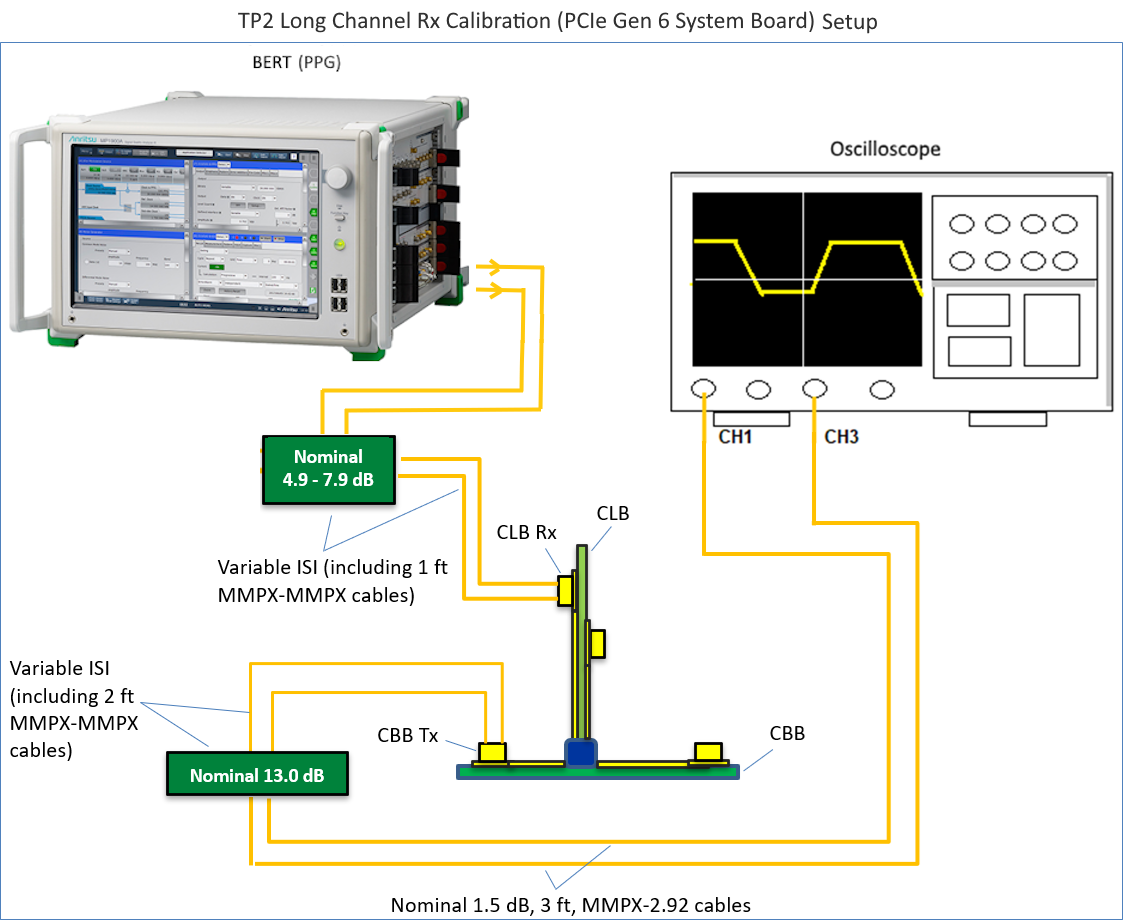

PCIe 5.0 规范中有应对挑战的指导原则。它对信号在传输过程中的削弱程度设定了限制(32 GT/s 时为 36 dB),误码率 (BER) 小于 10-12。为解决信号减弱或衰减问题,PCIe 5.0 对参考接收器进行了定义,以确保连续时间线性均衡器 (CTLE) 模型包括一个 -15 dB 的 ADC(可调直流增益)。而 16 GT/s 的参考接收器仅设置为 -12 dB。

当数据传输速率达到 32GT/s,误差频率会越来越高,尤其是 DFE 电路在接收器的整体均衡中起着至关键的作用。PCIe 5.0 架构中的预编码有助于抵消这一风险。在发送器侧启用预编码,在接收器侧启用解码,将大大降低突发错误的风险,并保证 PCIe 5.0 规范 32 GT/s 链路的稳健性。

PCIe 5.0 技术通道插入损耗预算

PCIe 4.0 和 PCIe 5.0 架构的插入损耗预算分别为 16 GT/s 和 32 GT/s。扣除 CPU 封装的 9 dB 后,剩余的预算分为 AIC 的 9.5 dB、CEM 连接器的 1.5 dB 和系统底板的 16dB。

除了插入损耗预算,工程师在设计 PCIe 5.0 时还需要考虑以下因素:

- PCB 线路的插入损耗随温度升高而增大

- 印刷电路板制造过程中的易变会在插入损耗中引起更大的波动,尤其是在线宽不一致的情况下

- 由于反射、串扰和电源噪声都会导致信噪比(SNR)的退化,必须为接收器留出额外的插入损耗余量。

在正常的情况下,硬件工程师和系统设计师会留出大约 10-20% 的整体信道插入损耗预算,即 36 分贝预算中大约 4-7 分贝。随着人工智能和 ML 需求的增加,预计会出现更多的系统拓扑结构。因此,工程师必须熟悉 PCB 材料和 PCIe 5.0 重定时器,以确保顺利升级到 PCIe 5.0 架构。

借助 GRL 的 PCIe 专家,往 PCIe 5.0 市场的顶尖冲

想要把新一代的AI 和 ML 技术产品设计技巧了如指掌,就赶快联络 GRL,借助我们经验丰富的专家智慧以及先进的测试设施。以确保您的产品满足不断改变的市场要求。