Josie Qie,GRL上海实验室

PCI-Express(Peripheral Component Interconnect Express),是一种高性能高带宽的串行通信标准,自PCIe推出以来,已经成为服务器(Server)和PC上的最重要的接口。PCIe以较低的生产成本,显著提升了系统的吞吐量,可扩展性和灵活性。为了实现更高的数据吞吐率,PCI-SIG协会不断更新传输速率,其发展如图1所示。

图1:PCIe标准的发展(来源:PCI-SIG)

随着信号传输速率的提升,信号传输过程中的损耗也更严重,多种因素的干扰包括信道质量、传输速率等,从而影响接收端对信号的判决。信号失真越严重,则误码率越高,进而影响通讯性能。为了在接收端获取易于判决的优质信号,可在发送端和接收端对信号进行补偿,保证其最大程度的在接收端收到可识别的信号眼图。对信号进行补偿的过程,称为信号均衡。

由于PCIe 1.0和PCIe 2.0使用的物理介质是普遍的FR4 PCB板材和廉价的接插件,为保证在该介质上的有效信号传输,PCI-SIG协会使用了8b/10b编码和发送端的固定参数的去加重(De-emphasis)均衡,其过程无需进行均衡参数协商。

在PCIe 1.0中,去加重值是固定值-3.5dB。

在PCIe 2.0中,去加重值是固定值-3.5dB 和 -6dB,无法动态调整。

随着速率增加到8.0GT/s及以上,信号传输过程中的完整性问题日益突出,仅采用传统的去加重方法无法实现高质量的信号传输,收发端间需要协商均衡系数来获得最优的传输性能。其次,为了继续使用传统的FR4板材和廉价的接插件,且兼容原有的1,2代设备,PCI-SIG协会对规范做了2方面改进:

使用128b/130b编码替代8b/10b编码,大幅提高了编码效率

使用动态均衡技术替代静态均衡技术。通过动态调整均衡的设置,使其在接收端获得最优的眼图,该动态均衡技术在规范中称作链路均衡(Link Equalization,LEQ)

PCIe 3.0 & PCIe 4.0 & PCIe 5.0 链路均衡

在链路训练(link training)之后,所有PCIe设备可能会进行链路均衡过程来建立设备间稳定的连接。链路均衡是一个链路优化过程,通过调节Tx (传输端)和Rx (接收端)的设置,提高信号质量,使PCIe链路以最稳定且更快的速率传输。链路均衡适用于支持PCIe Gen3 及以上的设备,且由于PCIe在Gen3及以上的每一代均需优化连接,因此链路均衡过程可能发生多次。例如:若所有PCIe设备为Gen5,则有3次链路均衡过程(第1次:Gen1-Gen3;第2次:Gen3-Gen4;第3次:Gen4-Gen5)。链路均衡通过PCIe 规范中定义的preset值来实现,preset指不同的预过冲(Preshoot)和去加重(De-emphasis)的组合。对于Gen3和Gen4,有11个preset值,即preset0-preset10。对于不同的链路情况,系统要求Rx端发送Tx EQ preset设置请求给Tx端,让其做对应的preset均衡设置;Tx端发送Rx EQ均衡设置,要求Rx端做相应的设置,最终获得一个最优的均衡组合和Rx端的眼图。

对于不同端口的preset值,是通过链路均衡协商,直到通过phase 0-3给所有链路均衡过程协商出其最优的preset值。

链路均衡涉及上行端口(Upstream port)和下行端口(Downstream port)之间的精确动态协商,该协商过程是在一定的时间范围内,去调整优化Tx端和Rx端的均衡滤波器,因此链路的误码率在BER ≤ 1E-12范围内运行。该协商过程同时发生在2个层面,一是电气子层(Electrical level),二是逻辑子层(Protocol level)。链路均衡在PCIe结构中所处位置如图2所示。

图2:链路均衡在PCIe中的架构(来源:PCI-SIG)

电气子层

Tx端均衡:

预加重(Pre-emphasis):PCIe高速串行信号在信道传输中,由于高频分量的衰减大于低频分量,造成信号失真,且高频分量主要集中于信号的上升沿和下降沿。为了补偿信号中高频成分的衰减,预加重在信号发送时,提高跳变沿的信号幅度,来提升高频分量。

去加重(De-emphasis): 由于信号中高频成分衰减大于低频,去加重是降低跳变沿 之外的信号幅度,即降低低频分量。

FFE (Feed-forward Equalizer) 前向反馈均衡器: FFE通常利用有限冲激响应滤波器 实现,即将延时的信号按不同的权重相加。通过控制权重的大小可调整均衡强度。FFE提高信号中的高频分量,来实现信道补偿。

Rx端均衡:

CTLE (Continuous-Time Linear Equalizer): 连续时间线性均衡器。CTLE均衡器类似无源高通滤波器,CTLE使得信号低频分量被抑制,导致信号高频分量与低频分量幅值区别缩小。缺点是会衰减信号中的低频成分,并放大了传输系统的高频噪声,会恶化系统的信噪比。

DFE (Decision Feedback Equalizer) 判决反馈均衡器。位于线性均衡器之后,是一种非线性均衡器。它由两个横向滤波器和一个判决器构成。两个横向滤波器分别为 前馈滤波器(Feed Forward Filter,FFF)和反馈滤波器(FeedBack Filter, FBF)。用于眼图张开的情况。此均衡器不会放大高频噪声,缺点是只能处理码后干扰,无法消除码前干扰,设计复杂,耗电。

FFE和CTLE可去除大部分由码间串扰引入的抖动,DFE可进一步去除码间串扰和部分由于阻抗失配所造成的反射。

逻辑子层

链路训练状态机LTSSM(Link Training and Status State Machine)如图3所示,位于PCIe结构中的物理层的逻辑子层内。

图3:LTSSM的主要状态转换图

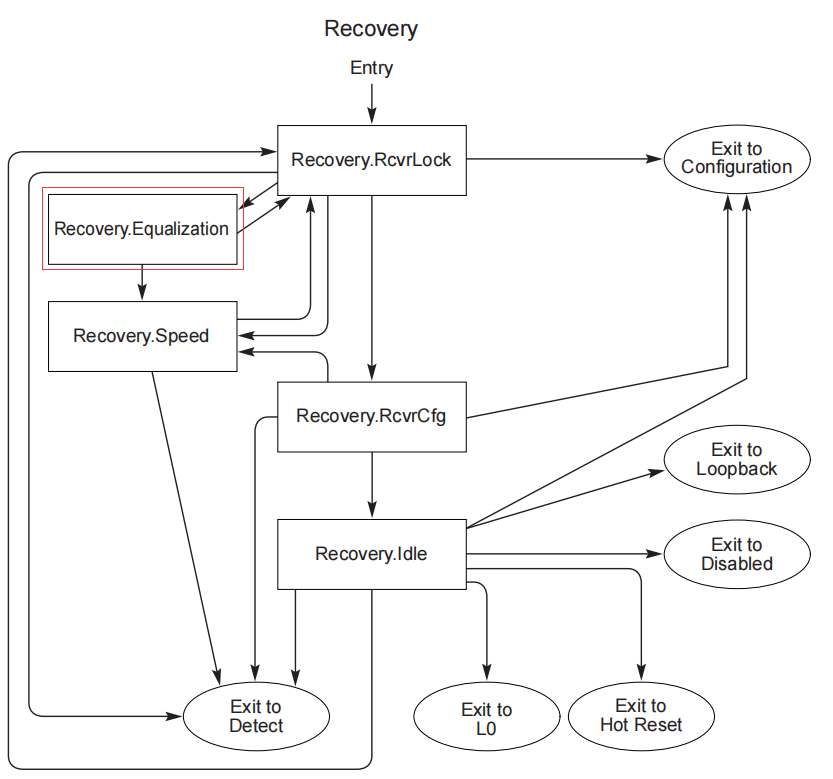

动态均衡协商发生在LTSSM中的Recovery子状态。通过该方式,来动态调整链路上的均衡设定值。通过动态的链路均衡,保证了链路的TX EQ为最优值,同时,本地端和对端也会同时调整RX EQ。通过TX EQ和RX EQ的动态调整,可实现灵活适应不同的信道。

上电后以2.5GT/s的速率依次从Detect – Polling- Configuration – L0 – Recovery。 由于USP(Upstream Port)和DSP(Downstream Port)在polling状态都声明支持8GT/s及更高速率,通过由USP(或DSP)发起调速请求,DSP(或USP)发起均衡请求,然后在Recovery状态开始调速和均衡。

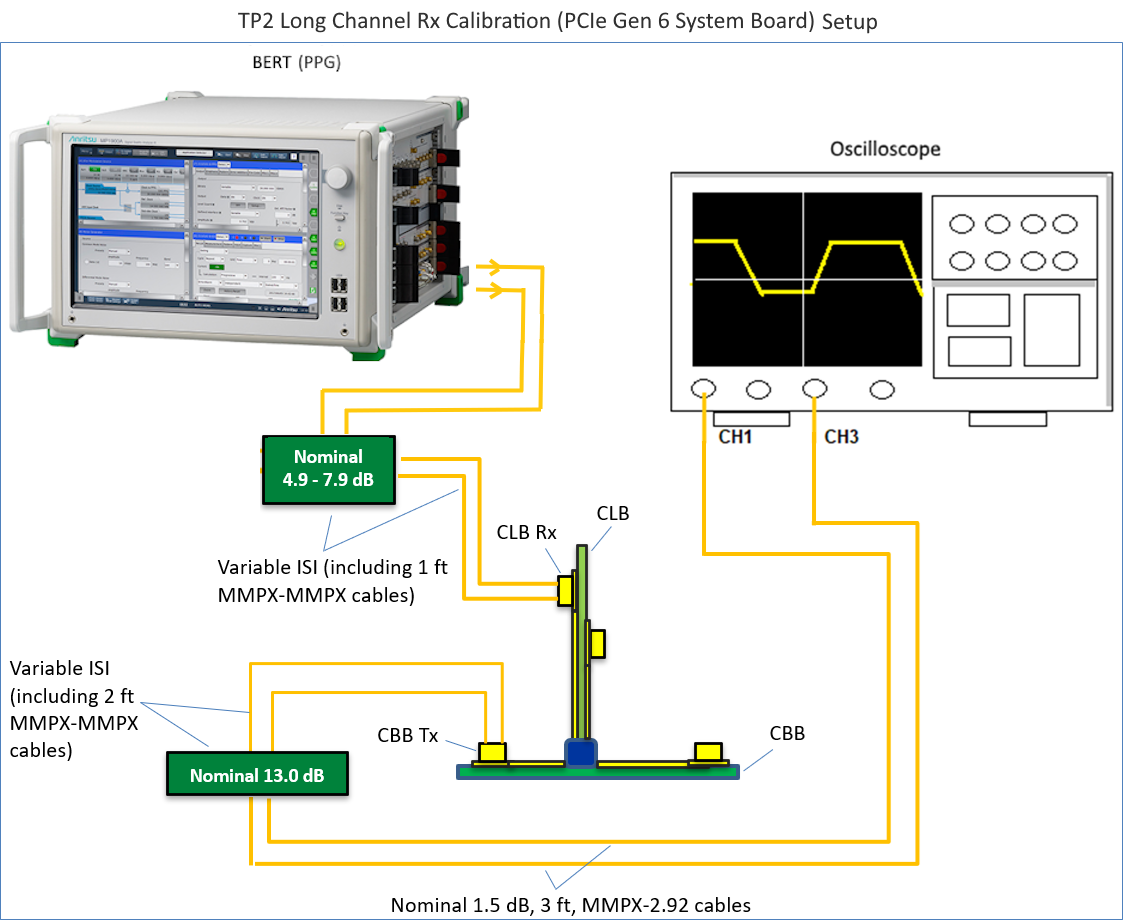

PCIe均衡系数协商

收发端在链路训练的过程中进行Tx/Rx端参数的动态协商,是在LTSSM Recovery状态中的Recovery.Equalization里。均衡系数的协商包括4个阶段,即Phase 0-3 (DSP:Phase1-Phase3; USP: Phase0-Phase3),其中Phase 2 和 Phase3 是可选择的。Recovery子状态转移如图4所示。

图4 Recovery子状态转移

Phase0:链路均衡的第一阶段。DSP给USP的每条lane发送所需的传输端preset值,这些preset值通过TS2(Training Sequence 2)训练序列传达。USP在接收到DSP的请求后,USP提升链路的数据传输速率至Gen3(8 GT/s),并发出包含有其收到的preset值的TS1(Training Sequence 1)训练序列返回至DSP。当Gen3的连接实现后,链路均衡将进入Phase1。

Phase1:尽管有出现链路质量差的可能性,但相同的TS1会被重复发送,来确保DSP接收到正确的preset值。这是为了充分优化链路,以便能够交换TS1并且完成用于精调目的的剩余链路均衡阶段。当链路的误码率实现BER≤10e-4 ,链路均衡进入Phase 2。

Phase2:DSP通过TS1发送均衡请求去调整USP的preset值,直至获得最优设置,链路的误码率应满足BER ≤ 1E-12。

Phase3:USP通过TS1发送均衡请求去调整DSP的preset值,直至获得最优设置,链路的误码率应满足BER ≤ 1E-12。

当Phase3完成后,链路均衡也完成了,且PCIe链路的误码率应满足BER ≤ 1E-12。然而,对于一些有长信道链路的主板设计,这种信号质量无法实现,可能需要另外的信号调节。在这种情况下,中继器(如ReDriver,ReTimer)被用来做信号调节,并在PCIe设备和Root complex(在CPU,存储设备和PCIe设备之间的重要连接部分)之间提供高质量信号。此时链路以Gen3的速率进入L0状态,并在该速率进行稳定通信。对于更高的传输速率,PCIe设备必须进行多次链路均衡过程。

2.3.1 8GT/s时,DSP与USP的均衡系数协商过程如图5所示

图5:8GT/s 动态均衡流程图

2.3.2 16GT/s时,DSP与USP的均衡系数协商过程如图6所示

图6:16GT/s 动态均衡流程图

多种均衡模式

最传统的PCIe均衡模式为全均衡模式(Full Equalization Mode)。在某一指定目标速率的链路训练中,通常采用全均衡模式,从低速率的均衡开始,再进行较高速率的均衡,直到完成目标速率的均衡。由于PCIe传输速率不断加倍,均衡的次数不断增加,耗时更多,影响系统性能。为节省均衡的耗时,从Gen5起,PCIe支持跨越其中间速率的均衡。对于原生传输质量极好的链路,也可关闭均衡。

Equalization bypass to highest rate

当双方设备均支持并且开启了Equalization bypass to highest rate时,才可跳过中间速率的均衡。在链路训练过程中,双方设备在LTSSM的Configuration状态通过交换TS序列来协商是否使用Equalization bypass to highest rate模式。若协商后选择该模式进行链路训练,则只进行一次切速,即当链路在2.5GT/s的L0状态后,进入Recovery直接切速至最高速率(32GT/s及以上),进行一次均衡。若最高速率均衡失败且重复均衡也失败,则须考虑降速。

No equalization needed

若双方均支持32GT/s及以上速率,且支持No equalization needed,在链路质量极好或本地存有之前均衡preset值的前提下,可选择该模式,不做EQ,以最快速度建立连接。在链路训练过程中,双方设备在LTSSM的Configuration状态通过交换TS序列来协商是否使用No equalization needed模式。

均衡结果判断

针对PCIe3.0及以上的传输速率,判别均衡是否成功,本质是看传输的误码率。在某个传输速率下,单独调整每一条Lane的收发端均衡器系数,使得链路上所有有效Lane上的传输误码率满足BER ≤1E-12,则认为该传输速率均衡完成,若在特定的响应时间内无法达到该指标,则该速率均衡失败。关于最大响应时间,Base(PCI Express Base Specification Revision 4.0 Version 0.7)规定值为500㎱,CEM(PCI Express Architecture PHY Test Specification, Revision 4.0, Version 1.0)规定值为1㎲。从过程上判断,均衡成功即LTSSM.Equalization完成了Phase0 – Phase 3的转换并正常进入了下一状态。

结论

PCI-Express是一种高速串行计算机扩展总线标准。PCIe设备要经过链路训练,来建立Root complex和不同PCIe 设备之间的连接。PCIe设备被允许以Gen1(2.5GT/s)的传输速率来发送和接收数据。若所连接的全部PCIe设备支持Gen3(8GT/s)及以上的速率,PCIe设备将进行链路均衡过程来建立更高速率的PCIe链路。链路均衡经过4个阶段的调节,允许在该误码率BER ≤ 1E-12条件下,以稳定支持的最高速率来传输数据。

参考文献

- PCI Express Architecture PHY Test Specification, Revision 3.0

- PCI Express Architecture PHY Test Specification, Revision 4.0, Version 1.0

- PCI Express Architecture PHY Test Specification, Revision 5.0, Version 1.0

- PCI Express Base Specification Revision 4.0 Version 0.7

作者

GRL上海测试工程师 郄雅楠 Josie Qie

诺丁汉大学电子通信和计算机工程硕士研究生。具有USB、SATA、PCIe等相关高速总线测试经验,协助客户解决测试问题并且取得认证。