充分利用 GRL 的深厚 DDR 专业知识、专业咨询和领先思维,解决您最棘手的内存设计与验证难题。

我们所提供的 DDR 至 DDR5、LPDDR 至 LPDDR5、以及传统 Host 和 DIMM 服务包括:- JEDEC 信号质量合规性测试

- DDR 性能和定制测试

- PCB 信号完整性测量与分析

- 调试与故障排除支持

- 测试方法、设置与探针咨询

- 内存总线设计与验证咨询

- 采用 Keysight Technologies EDA 解决方案的 DDR 建模与仿真

- DDR3 和 DDR4 DIMM/SODIMM 测试

- 内存通道验证审核

- 嵌入式内存测试("Memory Down")

- 针对高性能应用程序的内存分析,包括裕量测试、电源管理分析、数据总线利用率分析、Bank Group 分析以及显示长时间性能的汇总模式

DDR 测试

DDR 介面总览

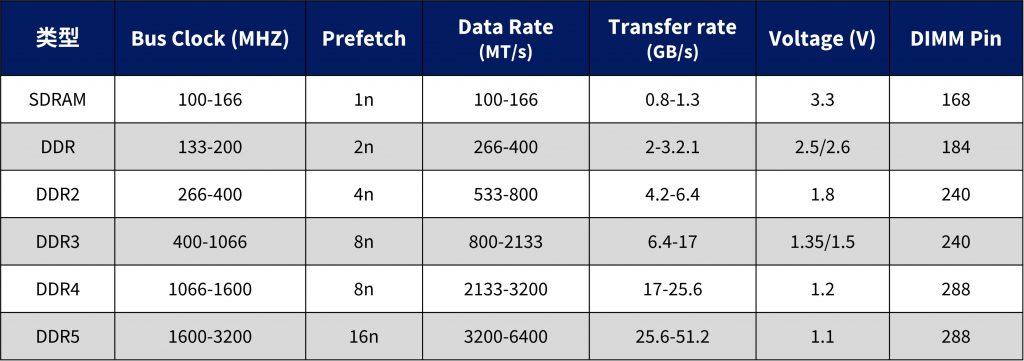

Double Data Rate,DDR 为内存传输标准,用名称直译也能帮助理解:每个时间脉冲周期(clock cycle)有双倍资料传输。内存规格,从初期的DDR、DDR2、DDR3、DDR4演进到 DDR5。不同的DDR 标准,会有不同的针脚、传输速度、功耗等。

JEDEC 协会

全称为 JEDEC Solid State Technology Association,固态技术协会,成立于1958年,是微电子产业的主导标准机构,且JEDEC 不隶属于任何一个国家或政府实体。JEDEC主要任务在标准化固态储存器(SSD)、DRAM、快闪记忆卡(Flash card)、无线射频辨识(RFID)等产品的生产、测试、功能定义。更多讯息请参考https://www.jedec.org

新版 DDR 规格

由于DDR每种版本的spec都不同。请输入JEDEC帐号 & 密码后到以下网址查询: https://www.jedec.org/standards-documents

DDR 标准术语

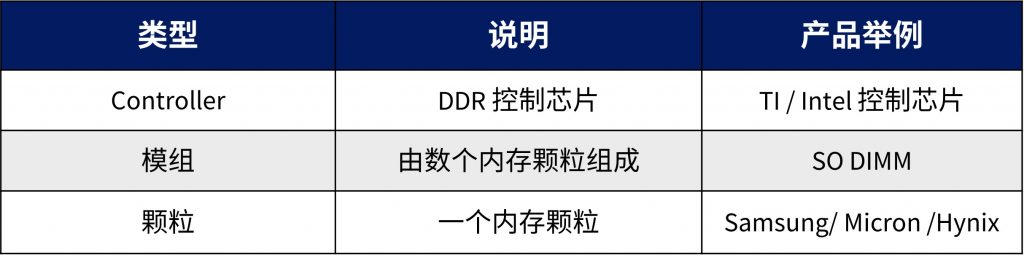

GRL 可以测试的 DDR 产品类型及范例

DDR 测试流程

DRAM 组件上必须安装中介层以便探测 DDR 信号。 如果能提供 S 参数,则中介层可以解嵌。GRL 所提供的额外收费服务包括选择和安装 DDR 中阶层。

客户需要提供的设备:

- 每款测试组件的精确 DQ(数据位)、DQS(选通脉冲)和 A(地址位)。

- 主机(Host)控制器系统

- 生成特定数据流的软件工具,

能够以安装了中介层的芯片颗粒为目标,在测试期间尽可能多地使用 DQ 和地址位。

DDR 数据流要求:

- DDR 仅使用随机数据和不少于8个字节的数据块进行写入。为了在突发传输中获得更多的 b0 和 b1 以生成 DDR 眼图,数据必须保持随机性。测试 DDR5则需要至少涵盖200个时钟周期的数据流。

- DDR 只能读取随机数据和不少于8个字节的数据块。提供的脚本可以是对指定位置执行随机写入,然后开始无限突发读取。

- 用于测试 JEDEC 规范的最佳数据流是 DDR 数据块的连续读写交替模式。

DDR 测试项目

DDR 2-3/LPDDR 2-3:

- 设置 1:DQ/DQS 读取和写入、CS# 和时钟

- 设置 2:地址、CAS#、RAS# 和 WE#

DDR 5/DDR 4/LPDDR 4/LPDDR 4x:

- 差分配置:时钟#、DQS#、DQ-x 读取和写入、命令(地址-x 或 CS#)

- (可选项目)单端配置:时钟和/或 DQS

LPDDR 5:

- 差分配置:Clock#、RDQS#、DQ-x 读取和写入以及 WCK#

- (可选项目)单端配置:Clock#、RDQS# 和/或 WCK#

- (可选项目)接收器物理层

如果想控制测试成本,可以仅在 DIMM 端执行写入信号的测试。或仅在 Host 端进行读取信号的测试,或降低待测数据的选择配置。

DDR 测试所需仪器

DDR 测试设备

- Keysight 或 Rohde & Schwarz RTP 16GHz 实时示波器

- 差分探头

- DDR 合规测试自动软件